17. Verilog HDL로 순차회로 설계하기 (Sequential Circuit)

순차회로

기존의 조합회로에 메모리 요소를 더한 것을 순차회로라 한다. 이때 메모리 요소로는 주로 D-FF이 사용된다. 이를 통해 회로에는 CLK이 추가되게 된다.

always @ (a or b or sel) //조합회로

always @ (posedge clk) //순차회로이제 우리는 값의 변동을 CLK을 이용해서 처리할 것이다.

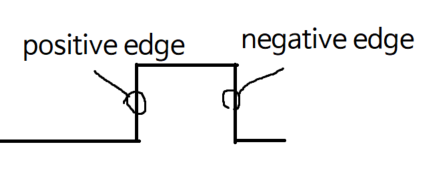

Positive/Negative Edge Clock

신호가 0에서 1이 되는 시점을 Positive Edge, 1에서 0이 되는 시점을 Negative Edge라 한다.

위 코드에서 순차회로에 사용된 것은 Edge-Triggered FilpFlop이며, posedge, positive edge를 이용하여 Trigger된다.

Race Condition

두 개 이상의 always 블록이 있을 경우, 이들은 모두 평행하게 실행되므로, 각 블록이 동시에 하나의 값을 다룬다면 예측불가한 값이 나올 수 있음에 유의해야 한다!

D-flipflop의 동기/비동기 초기화

동기 초기화에서는 CLK 주기에 맞춰서만 값이 변동, 그러나 비동기 초기화의 경우 CLK과 관계없이 reset 입력이 바뀌면 바로 적용.

동기 초기화 (Synchronous)

CLK의 edge에서 reset 신호에 따라 reset

always @ (posedge clock)

begin

if (reset) data <= 1'b0

else data <= data_in

end비동기 초기화 (Asynchronous)

Reset의 edge에서 reset. 이때, edge condition과 if 조건문의 극성이 일치해야 함.

always @ (posedge clk or negedge reset) # reset이 1에서 0으로 갈 때

begin

if (!reset) # reset이 0이면 리셋

data <= 1'b0

else

data <= data_in

end

always @ (posedge clk or posedge reset) # reset이 0에서 1로 갈 때

begin

if (reset) # reset이 1이면 리셋

data <= 1'b0

else

data <= data_in

endBlocking / Non-blocking Assignment

=를 이용한 할당을 Blocking Assignment, <=를 활용한 할당을 Non-blocking Assignment라 한다.

Blocking Assignment

Blocking Assignment는 해당 구문이 등장한 시점에 할당이 이루어진다. 즉, 코드의 작성순서대로 실행되는 것이다. 먼저 작성된 코드가 끝날 때까지 뒤쪽 코드는 '블록'당한다.

Non-blocking Assignment

Non-Blocking Assignment는 CLK의 마지막 주기에 할당이 이루어진다. 이 방법으로 작성된 코드들은 모두 마지막에 한번에 할당된다.

예시

a = b; //blocking

b = a;

// a와 b는 모두 b이다.

a <= b; //non-blocking

b <= a;

// a와 b는 swap된다.'학부 수업 > 디지털시스템' 카테고리의 다른 글

| 19. Read-Only Memories: ROM (0) | 2020.05.24 |

|---|---|

| 18. 3 상태 버퍼 (Tristate Buffer) (0) | 2020.05.24 |

| 16. Verilog HDL의 산술 연산과 Incomplete Specification (0) | 2020.05.23 |

| 15. Verilog HDL을 이용한 7-seg display Decoder 구현 (0) | 2020.05.23 |

| 14. 하드웨어 기술 언어와 Verilog HDL(Hardware Description Language: HDL) (0) | 2020.05.22 |

댓글

이 글 공유하기

다른 글

-

19. Read-Only Memories: ROM

19. Read-Only Memories: ROM

2020.05.24 -

18. 3 상태 버퍼 (Tristate Buffer)

18. 3 상태 버퍼 (Tristate Buffer)

2020.05.24 -

16. Verilog HDL의 산술 연산과 Incomplete Specification

16. Verilog HDL의 산술 연산과 Incomplete Specification

2020.05.23 -

15. Verilog HDL을 이용한 7-seg display Decoder 구현

15. Verilog HDL을 이용한 7-seg display Decoder 구현

2020.05.23